Probar placas de circuito impreso (PCB) a lo largo de los procesos de diseño y fabricación es esencial para garantizar productos de calidad. Evita situaciones en las que los diseñadores y fabricantes se dan cuenta de que el producto está defectuoso en el último minuto, mientras los tableros están en plena producción o ya en el mercado.

Incluso después de seguir los procesos de diseño y fabricación adecuados, siempre existe el riesgo de defectos, errores, errores humanos en las etapas del prototipo. Identificar y abordar estos problemas antes del producto final es fundamental para garantizar el rendimiento, la funcionalidad y la confiabilidad de los productos. Puede surgir una amplia gama de defectos en los PCB debido a errores humanos, un proceso de fabricación incorrecto, un diseño deficiente y otras prácticas.

Los beneficios de las pruebas incluyen

- Identificar y abordar fallas y errores como cortocircuitos, aperturas, soldadura deficiente, problemas funcionales y más.

- Brinda la oportunidad de abordar cualquier problema potencial temprano antes de pasar a la producción final, lo que ahorra tiempo y dinero. Arreglar los problemas de los productos terminados suele ser más difícil, lento y costoso.

- Reducir el desperdicio y los costos, ya que los probadores utilizan ensamblajes y prototipos a pequeña escala en lugar de productos completos. Esto evita desechar ensamblajes defectuosos a gran escala.

Probar PCB

Una PCB consta de varias partes y componentes diferentes. Cada uno de estos tiene un impacto en el rendimiento general del circuito y el conjunto de la electrónica en su conjunto. Idealmente, es importante probar todo. Esto incluye, pero no se limita a verificar;

- Conductividad eléctrica

- Fuerza mecánica

- Calidad de soldadura

- Limpieza

- Pruebas para el entorno de destino

- Laminación – fuerza de pelado

- Calidad de la pared del agujero

- Colocación de componentes, alineación, polaridad, orientación, etc.

Técnicas de prueba de PCB

Por lo general, las pruebas implican verificar las características del diseño en términos visuales, estructurales, eléctricos y funcionales. En la mayoría de los casos, existen varias técnicas para probar cada una de estas áreas, y la elección depende de factores como la complejidad de la placa, la aplicación, el diseño, etc. Los métodos comunes incluyen;

- Pruebas en circuito (ICT)

- Escaneo de límites JTAG

- Inspección óptica automatizada (AOI)

- Inspección automatizada de rayos X (AXI)

Los equipos de prueba pueden usar métodos de inspección visual manual (MVI) o equipos de prueba automatizados (ATE) para verificar los PCB después del proceso de ensamblaje. Sin embargo, los métodos de prueba automáticos, como el AOI de inspección óptica automatizada y la inspección de rayos X automatizada (AXI) son más efectivos para las pruebas de nivel de ensamblaje, pero generalmente son costosos.

Además de las pruebas visuales y eléctricas en los contactos, algunas aplicaciones como las industrias militar, aeroespacial, minera y similares requieren pruebas mecánicas. Esto asegura que el BGA y otros componentes resistirán los golpes, vibraciones y otras condiciones adversas en los entornos operativos. En la mayoría de los casos, las pruebas son destructivas e implican someter la PCB a fuerzas de choque y cizallamiento. La medición de la deformación ayuda a establecer las propiedades mecánicas de las juntas de soldadura.

Pruebas en circuito (ICT)

El ICT comprende un probador en circuito, un accesorio y el software y puede cubrir la mayoría de los defectos que ocurren durante los procesos de fabricación. Los probadores pueden usarlo para verificar cortocircuitos, aperturas, resistencia, capacitancia e inductancia, además de verificar la polaridad u orientación de dispositivos como diodos, transistores e circuitos integrados.

Las pruebas en circuito verifican los componentes basándose en un modelo del diseño. Teóricamente, tiene el potencial de detectar aproximadamente el 98% de las fallas de PCB. Sin embargo, esto puede no ser posible en la práctica, especialmente cuando no puede acceder a todos los nodos, así como su incapacidad para medir valores de capacitancia e inductancia muy bajos.

Los beneficios de las TIC incluyen la detección de defectos, la programación y los informes de prueba fáciles de interpretar. Sin embargo, tiene inconvenientes como equipos costosos, dificultades para actualizar los sistemas de los equipos de prueba ya que se fijan mecánicamente, imposibilidad de acceder a algunos nodos en circuitos complejos, etc.

Las dos técnicas TIC más utilizadas son la cama de clavos y la sonda voladora . Cada uno tiene su lugar, beneficios y limitaciones, y la elección depende de la naturaleza y complejidad de la PCB bajo prueba.

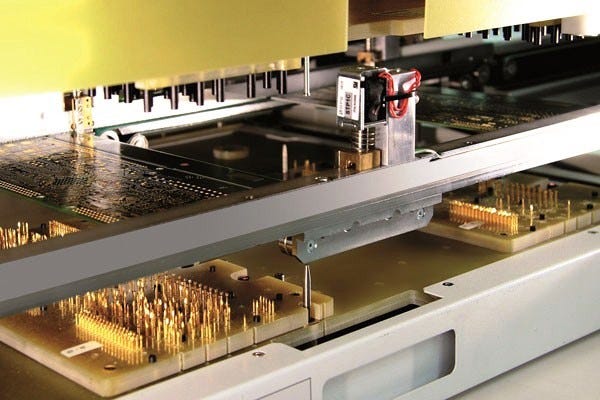

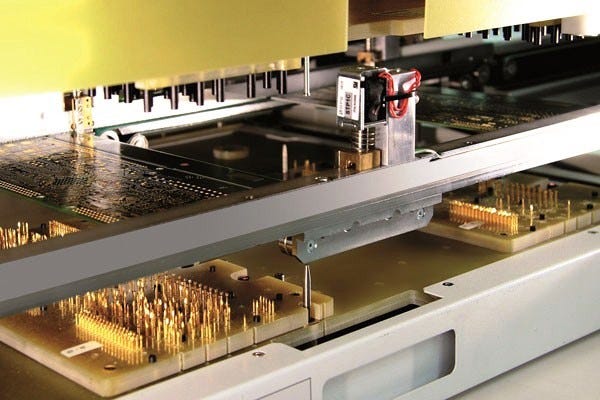

Técnica de cama de uñas

El lecho de clavos o las pruebas en circuito de la rejilla universal se basan en múltiples pines pogo cargados por resorte que hacen contacto con varios puntos de la PCB. Estos alfileres se asemejan al lecho de clavos, de ahí el nombre. En la prueba, cada uno de los pines pogo hace contacto con el nodo del circuito o el punto bajo prueba. Este método puede identificar, cortocircuitos, aperturas, puentes de juntas de soldadura, componentes defectuosos y otras fallas de PCB.

Una prueba típica en circuito consta de varios pines repartidos por la placa. La aplicación de múltiples pines asegura decenas o cientos de conexiones y pruebas simultáneas. Cada uno de estos tiene aproximadamente 35 mm de largo y generalmente se inserta en el extremo de una red, como una plataforma de montaje en superficie, un orificio o un punto de prueba. Con todas las redes conectadas, la prueba dura unos 7 segundos.

Durante la prueba, los pines introducen algunas señales y voltajes en el circuito, después de lo cual miden los valores resultantes en la línea.

Generalmente, la técnica del lecho de clavos es un método de prueba rápido y de bajo costo que es adecuado para sistemas de producción en masa, circuitos simples y placas analógicas. Sin embargo, puede estar limitado cuando se trabaja con placas complejas y especialmente aquellas con anchos de paso pequeños, SMD, BGA y componentes similares.

Prueba de sonda voladora

La técnica utiliza un elemento con un paso más pequeño para hacer contacto con los puntos de prueba, como los pines SMD. Esto es adecuado para contactos de tamaño pequeño hasta un paso de prueba de 0,2 mm. En la práctica, utiliza varias sondas para hacer contacto con los pines, las almohadillas y las vías y probar si hay aperturas, cortocircuitos y parámetros eléctricos como la polaridad, la resistencia y la capacitancia.

Algunos equipos de prueba pueden incluir una cámara para determinar si faltan componentes y analizar los tamaños, formas, orientación, polaridad y otras propiedades físicas de los componentes.

Inspección óptica automatizada (AOI)

El método AOI utiliza una o varias cámaras para analizar ópticamente la PCB. Utiliza software para comparar las imágenes de la PCB bajo prueba con las de una placa de referencia similar. Otra opción es comparar con especificaciones de diseño ideales. La inspección óptica generalmente se realiza al final de la línea de ensamblaje, donde ayuda a verificar la calidad del producto terminado.

Además de realizar pruebas en la PCB en ensamblaje, el método AOI puede monitorear el proceso de fabricación. El uso de la tecnología en las máquinas de recogida y colocación permite a los fabricantes realizar un seguimiento de los procesos en tiempo real y corregir defectos de montaje, como posibles errores de colocación y alineación de los componentes.

En algunas aplicaciones, la inspección óptica implica el uso de un endoscopio para ver las conexiones entre el BGA y la PCB.

El método AOI solo es útil en PCB donde los puntos a probar son ópticamente visibles.

Inspección automatizada de rayos X (AXI)

AXI proporciona una técnica de prueba no destructiva con la capacidad de detectar defectos de soldadura invisibles para el ojo humano o cuando se utiliza la inspección óptica automática. No requiere una conexión física y puede encontrar defectos en los grandes paquetes de IC como BGA, Micro BGA, QFN, LGA, CSP, etc.

Generalmente, la técnica de rayos X es adecuada para probar áreas invisibles ubicadas en el centro. El método se basa en la capacidad de los materiales para absorber los rayos X de acuerdo con su espesor y número atómico. Debido a que la tasa de absorción es directamente proporcional al peso atómico del elemento, los materiales más pesados, como la soldadura, generalmente absorben más rayos X y son más visibles. Los elementos más ligeros, como el paquete de circuito integrado, parecen más transparentes porque absorben menos rayos X.

A continuación se muestra una imagen de rayos X típica de un BGA. Las secciones relativamente transparentes se refieren a materiales más claros, mientras que las partes más oscuras reflejan partes más pesadas como la soldadura.

Como tal, los rayos X pueden penetrar el paquete de CI e inspeccionar la soldadura y las conexiones donde identifica defectos estructurales como cortocircuitos, aperturas, soldadura insuficiente, exceso de soldadura y vacíos.

Otras capacidades incluyen la comprobación de

- Mala alineación para el BGA y otros chips grandes

- Conexiones que no son simétricas

- Consistencia de la altura de separación del paquete

- Palomitas de maíz: que ocurre cuando algunas bolas se fusionan para formar formas irregulares.

- Análisis de soldadura donde se comprueba el interior de la soldadura para identificar defectos como burbujas, llenado insuficiente, etc.

El método es ideal para verificar la placa, sus capas, soldadura, orientación de componentes, alineación y otras características físicas.

Elegir una solución de prueba de PCB

Las técnicas varían según el tipo de PCB, las pruebas a realizar, la aplicación, la sensibilidad y la tolerancia. Por ejemplo, las aplicaciones médicas, aeroespaciales, militares y similares requieren niveles más altos de confiabilidad.

La mayoría de las veces, es fácil verificar una PCB simple, de una o dos capas utilizando métodos de prueba tradicionales. Sin embargo, a medida que aumenta el nivel de complejidad debido a las altas densidades de componentes, múltiples capas, miniaturización y otros factores, las pruebas requieren técnicas avanzadas como AOI y AXI .

Las pruebas en circuito funcionarán para la mayoría de los circuitos básicos, pero a medida que aumenta el nivel de complejidad y la densidad de los componentes, se vuelven necesarias otras técnicas como AOI y AXI. Los rayos X son adecuados para PCB con chips grandes como los BGA y otros en los que algunas conexiones son invisibles incluso cuando se utiliza el método óptico.

La prueba de las placas de circuito impreso durante las etapas de fabricación brinda a los diseñadores la oportunidad de identificar defectos y otros problemas que podrían afectar el rendimiento del producto final. Abordar los defectos antes del producto final es mucho más fácil, menos costoso y es una estrategia eficaz que mejora la calidad al tiempo que reduce costosas reparaciones, retiros y desperdicio de material.

Aunque una combinación de todas las técnicas proporcionará de manera espectacular un análisis completo y la identificación de casi todos los defectos, es importante buscar la solución más rentable.

Pruebas de escaneo de límites para circuitos integrados y ensamblajes de PCB

Cuando se trata de probar un conjunto de circuito, puede probar con simulación y puede probar en circuito. Una prueba de escaneo de límites es algo completamente diferente, lo que le permite probar el estado de las trazas individuales mientras el circuito está activo.

Una prueba de escaneo de límites es una técnica para verificar circuitos integrados e interconexiones en PCB. Sigue una arquitectura y procedimientos de prueba definidos por el Joint Test Action Group (JTAG) bajo el estándar IEEE 1149.1.

La prueba de escaneo de límites (BST) o JTAG, permite la prueba de circuitos integrados y placas complejas donde el acceso físico a los pines es difícil o imposible cuando se utilizan otros métodos. En lugar de sondear mecánicamente cada pin, el BST se basa en una interfaz de hardware de cuatro cables para enviar y recibir señales de prueba específicas en los circuitos integrados y las placas bajo prueba.

A diferencia de otros métodos de prueba que requieren equipos de prueba costosos, la técnica de escaneo de límites se basa en la lógica y utiliza herramientas de prueba mínimas y es menos costosa y más efectiva. Además, la técnica no requiere mucho acceso físico y realizará pruebas exhaustivas siempre que el circuito esté diseñado de acuerdo con el estándar JTAG.

Esta metodología de prueba, que se desarrolló en los años 80 para el microprocesador Intel 80486, es hoy una técnica estándar que los fabricantes y profesionales utilizan para programar, depurar y probar casi todos los dispositivos y sistemas integrados. La mayoría de los fabricantes de semiconductores están agregando la lógica de prueba necesaria para verificar la funcionalidad del chip en el propio IC. Esto hace que sea más fácil verificar y encontrar defectos en circuitos integrados complejos como FPGA, CPLD, DSP y otros sin usar las sondas de prueba físicas.

Limitación de métodos de prueba comunes en circuitos complejos y densamente poblados

Hoy en día, el mercado de PCB se está desplazando hacia superficies más pequeñas, altas densidades de componentes, componentes complejos, más funcionalidades y ciclos de vida de productos más cortos. Los fabricantes utilizan cada vez más placas multicapa, matrices de rejilla de bola (BGA), tecnología de montaje en superficie (SMT), módulos de varios chips (MCM), sistemas en paquete (SIP), trazas de PCB más pequeñas, mayor número de pines IC, componentes de paso fino y otras tecnologías. Todo esto hace que sea significativamente más difícil probar el circuito durante el funcionamiento.

A pesar del aumento de las funciones y la complejidad, los fabricantes disfrutan cada vez más de lanzar productos más rápido para sobrevivir en el mundo competitivo. Con tales tendencias y demandas, el desarrollo y las pruebas de PCB se han convertido en un desafío.

Las tecnologías anteriores dificultan el acceso a los pines y, por lo tanto, limitan la efectividad de las pruebas en circuito (ICT) , las pruebas del equipo de prueba automático (ATE) y otras técnicas que dependen del sondeo mecánico. En particular, la falta de acceso directo a los pines, las uniones soldadas y los puntos de prueba dificulta la realización de algunas pruebas funcionales en los circuitos integrados y PCB grandes y complejos.

Aunque existen varios métodos de prueba, los fabricantes pueden optar por una combinación de técnicas que les ayuden a lograr una cobertura completa con el presupuesto adecuado.

De los principales métodos de prueba, las pruebas de escaneo de límites de JTAG proporcionan la mejor cobertura del espectro de defectos PCOLA / SOQ / FAM. En consecuencia, reduce la necesidad de métodos de prueba estructurales adicionales e incluso puede eliminarlos dependiendo de la PCB.

Arquitectura de escaneo de límites y cómo funciona

El estándar IEEE-1149.1 define la lógica de escaneo de límites de los circuitos integrados compatibles con JTAG. Un IC listo para JTAG típico se compone de celdas de escaneo de límites, también conocidas como celdas lógicas colocadas entre el sistema lógico del chip y los pines o bolas de señal. Cada celda tiene su función específica: la mayoría son solo de entrada o salida, pero algunas son bidireccionales.

Por lo general, las celdas se agregan en el límite del chip, entre la lógica del núcleo del IC y los pines de E / S o el límite, de ahí el nombre de escaneo de límites. Esto establece una ruta de datos de prueba en serie que se ejecuta a través de todo el IC. En el modo de prueba, las celdas controlan el estado del pin de salida mientras leen el del pin de entrada, lo que permite probar las interconexiones del circuito integrado y la placa. Las celdas suelen aparecer transparentes durante el modo normal.

Para que un componente cumpla con el estándar JTAG de escaneo de límites, debe incluir;

- Una celda de escaneo de límites para cada pin de E / S.

- La ruta de escaneo donde todas las celdas de límite están conectadas en serie

- Una interfaz de puerto de acceso de prueba (TAP) de cuatro o cinco cables y un controlador para manejar las señales de escaneo de límites. El quinto cable es opcional para proporcionar la señal de reinicio).

- Cuatro o cinco pines adicionales para las señales JTAG.

- Archivos de Lenguaje de descripción de exploración de límites externos (BSDL) proporcionados por el proveedor del componente. Estos describen los comportamientos de escaneo de límites, la información del paquete y las capacidades para un componente en particular, proceso de implementación, instrucciones, celdas de escaneo disponibles, advertencias de diseño, etc.

Controlador de puerto de acceso de prueba (TAP)

Un IC compatible con JTAG tiene un controlador de puerto de acceso de prueba (TAP) que consta de las cuatro señales y la lógica que las conecta y controla. El chip JTAG tiene cuatro cables o pines obligatorios y un quinto opcional para una señal de reinicio. Los pines y roles requeridos son;

- TDI: pin de entrada en serie para las instrucciones, pruebas y datos de programación

- TDO: pin de salida en serie para las instrucciones, pruebas y datos de programación

- TMS: entrada para la señal que gestiona la máquina de estado del controlador TAP.

- TCK: pin de entrada de señal de reloj para el circuito de escaneo de límites

- TRST- señal de reinicio (opcional)

El controlador TAP se compone de una máquina de estados finitos de 16 estados. Estos estados están controlados por el reloj de prueba (TCK) y las señales de selección de modos de prueba (TMS). La interfaz JTAG proporciona un medio para conectar las herramientas externas al controlador TAP incorporado.

Cómo funcionan las pruebas de escaneo de límites

En una prueba de escaneo de límites típica, el probador envía señales de diagnóstico al pin de entrada TDI del dispositivo. Las celdas de escaneo de límites capturan las señales y las desplaza en serie a través de la lógica central que también las escanea. Luego, la salida se desplaza en serie fuera del núcleo a través del pin TDO.

El último paso consiste en comparar la salida con el resultado esperado y, en consecuencia, identificar si hay cortocircuitos, aperturas, dispositivos faltantes, componentes muertos, defectos internos dentro de los componentes, etc.

Por lo general, la técnica de escaneo de límites permite a los ingenieros configurar las celdas en dos modos de prueba principales. Esto incluye el modo de prueba interno para verificar la lógica dentro del chip, mientras que el modo externo prueba las interconexiones entre los circuitos integrados en la PCB.

Diseño de una placa de circuito impreso para la prueba de escaneo de límites

Además de las pruebas internas de los circuitos integrados, los diseñadores pueden agregar la capacidad de escaneo de límites a nivel de placa. Diseñar para pruebas de escaneo de límites tiene muchos beneficios, especialmente para tableros que se utilizan en entornos hostiles, equipos que requieren reparación en el campo, cuando existe la necesidad de identificar puntos de falla para abordar con fines de rediseño, etc. En general, es una buena estrategia al diseñar para la capacidad de prueba.

Dicho diseño comienza seleccionando dispositivos compatibles con IEEE 1149.1 o JTAG y colocando un conector de bus de prueba en una ubicación accesible. Por ejemplo, para la tarjeta PCB, una buena estrategia es enrutar las señales del bus de prueba al conector de borde y asignarlas a los pines de repuesto.

En una PCB que utiliza muchos dispositivos compatibles, estos están conectados en cadena. La salida de un chip se convierte en la entrada del siguiente y así sucesivamente. La señal de prueba se aplica al primer IC de la cadena, mientras que la salida aparece en el último dispositivo. Esta disposición ayuda a verificar la continuidad de las conexiones entre los pines de los distintos componentes.

La lógica de escaneo de límites tiene un modo BYPASS que los probadores pueden usar para acortar la cadena y el tiempo de prueba. Además, un puente JTAG dedicado brinda la capacidad de configurar selectivamente la cadena de escaneo con múltiples ensamblajes o componentes.

Beneficios de las pruebas de escaneo de límites

Los beneficios del escaneo de límites incluyen, entre otros;

- Capacidad para probar circuitos integrados y PCB y con acceso limitado o nulo a las conexiones y pines internos.

- Reducir los esfuerzos, los costos y el tiempo de prueba de PCB sin comprometer la calidad. Además, ofrece patrones de prueba reutilizables, mejor cobertura de prueba y menor tiempo de comercialización.

- Proporciona depuración y programación en circuito de bajo costo de los CPLD, EEPROM seriales, Flash, memoria en chip, etc.

- Reduce el riesgo de dañar físicamente la PCB, los pines o crear cortocircuitos con las sondas mecánicas.

- La integración de las celdas JTAG a nivel de placa mejora la producción y las pruebas de campo al tiempo que elimina la necesidad de otros costosos procedimientos y equipos de prueba.

Inconvenientes de la tecnología de prueba de escaneo de límites

A pesar de los beneficios, la técnica de escaneo de límites tiene algunos inconvenientes, como la necesidad de silicio adicional para los circuitos de escaneo de límites, pines adicionales y más consumo de energía. Además, requiere más esfuerzos de diseño y los dispositivos pueden sufrir una degradación del rendimiento.

Si bien un escaneo de límites es útil para probar o reprogramar circuitos integrados y PCB, los delincuentes pueden usarlo para piratear dispositivos conectados como IoT. Los delincuentes pueden lanzar ataques físicos utilizando la interfaz JTAG como una puerta trasera para acceder y explotar los dispositivos. En consecuencia, los delincuentes pueden comprometer los datos, provocar un mal funcionamiento o detener el equipo.

Herramientas de escaneo de límites

Con la creciente aceptación del escaneo de límites como el método principal para probar interconexiones y realizar la programación en el sistema, varias empresas de hardware y software han desarrollado una amplia gama de herramientas. Hoy en día, existen varias herramientas maduras de hardware y software de JTAG en el mercado.

Las herramientas típicas de escaneo de límites o JTAG son;

- Corelis – ScanPlusTPG

- Teradyne – Victoria

- Acculogic – ScanManager

- Goepel Electronic – Sistema Cascon

- Activo InterTech – ScanWorks

- Intellitech – Entorno de desarrollo de pruebas Eclipse

- Flynn Systems – onTAP.

La prueba de escaneo de límites es una técnica de prueba de circuitos integrados y PCB rentable y más rápida con una cobertura más amplia en comparación con otros métodos. La técnica de escaneo de límites JTAG, que se basa en el estándar de la industria, IEEE 1149.1, proporciona una solución de prueba mejor, fácil y de bajo costo para PCB con acceso limitado a pines de componentes y circuitos a nivel de placa.

Tiene muchas aplicaciones, que incluyen pruebas, depuración y programación de una amplia gama de circuitos integrados y PCB complejos de la actualidad. Esto es aplicable durante todo el ciclo de vida de los PCB, que es durante el diseño, la producción y en el campo, lo que proporciona ahorros significativos en el desarrollo del producto, el tiempo de soporte y los costos.